ARM Cortex-A/R Integration Guide

Getting started

Integrating on an ARM Cortex-A or Cortex-R device follows the same workflow as on a Cortex-M device. Complete the steps in the guide linked below, then return here to implement any Cortex-A/R specific integration steps.

ARM Cortex-M integration guide

ARM Cortex-A/R specific steps

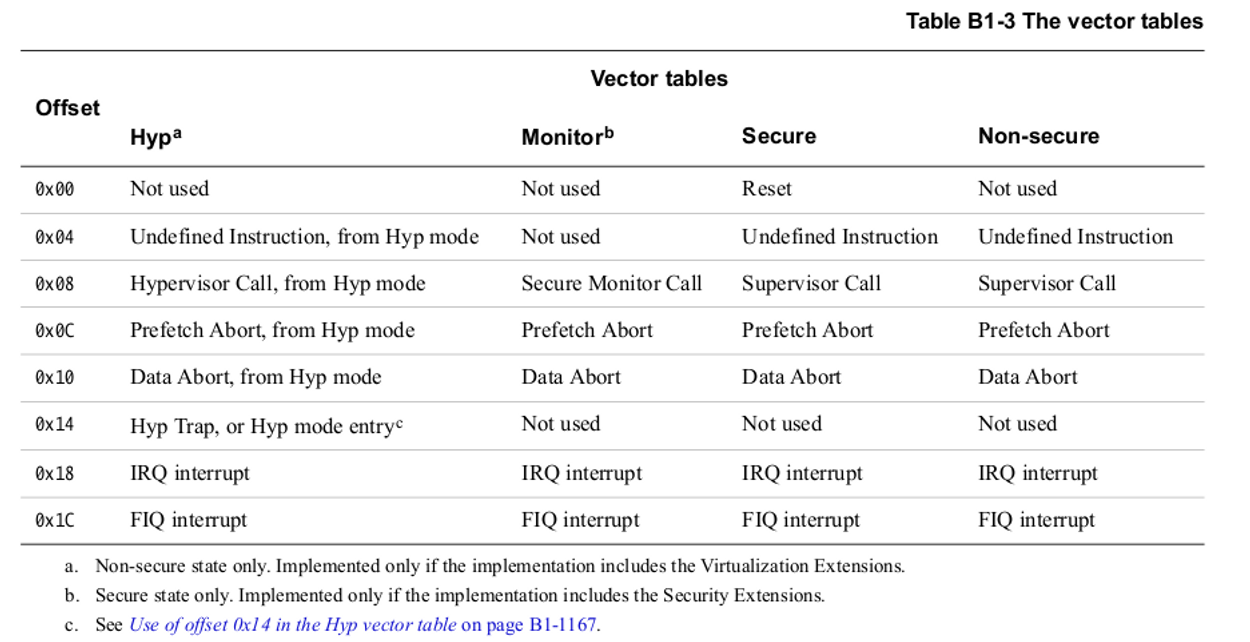

The ARMv7-A/R architecture has a different exception/interrupt handler dispatching mechanism as compared to Cortex-M devices (excerpt below is from the ARM Architecture Reference Manual ARMv7-A and ARMv7-R edition):

To integrate the Memfault fault handlers into the exception handlers, install the following functions into the program's vector table:

UndefinedInstruction_HandlerDataAbort_HandlerPrefetchAbort_Handler

If you need help instrumenting the fault handlers, don't hesitate to reach out to Memfault support!

These functions are defined in the Memfault Firmware SDK here.

An example vector table is show below:

/*-------------------------------------------------------------------------------*/

@ import reference for interrupt routines

.extern _c_int00

.extern phantomInterrupt

.weak resetEntry

@ Memfault Fault Handlers used in the interrupt vector table below

.extern UndefinedInstruction_Handler

.extern DataAbort_Handler

.extern PrefetchAbort_Handler

/*-------------------------------------------------------------------------------*/

@ interrupt vectors

resetEntry:

ldr pc, =_c_int00

ldr pc, =UndefinedInstruction_Handler /* Memfault handler */

svcEntry:

b svcEntry

ldr pc, =PrefetchAbort_Handler /* Memfault handler */

ldr pc, =DataAbort_Handler /* Memfault handler */

b phantomInterrupt

ldr pc,[pc,#-0x1b0]

ldr pc,[pc,#-0x1b0]

You should be able to see the correct addresses when dumping the .intvecs

section (or whatever the vector section is called in your program).

$ arm-none-eabi-objdump --disassemble -j .intvecs ./build/memfault.elf

./build/memfault.elf: file format elf32-littlearm

Disassembly of section .intvecs:

00000000 <resetEntry>:

0: 18 f0 9f e5 18 f0 9f e5 ........

00000008 <svcEntry>:

8: eafffffe b 8 <svcEntry>

c: e59ff014 ldr pc, [pc, #20] ; 28 <svcEntry+0x20>

10: e59ff014 ldr pc, [pc, #20] ; 2c <svcEntry+0x24>

14: ea00246f b 91d8 <phantomInterrupt>

18: e51ff1b0 ldr pc, [pc, #-432] ; fffffe70 <_estack+0xf7fbfe70>

1c: e51ff1b0 ldr pc, [pc, #-432] ; fffffe74 <_estack+0xf7fbfe74>

20: 0000b598 .word 0x0000b598

24: 00012cf4 .word 0x00012cf4

28: 00012d70 .word 0x00012d70

2c: 00012d3c .word 0x00012d3c

$ arm-none-eabi-addr2line --exe ./build/memfault.elf 0x00012cf4 0x00012d70 0x00012d3c

./third-party/memfault-firmware-sdk/components/panics/src/memfault_fault_handling_armv7_a_r.c:315

./third-party/memfault-firmware-sdk/components/panics/src/memfault_fault_handling_armv7_a_r.c:339

./third-party/memfault-firmware-sdk/components/panics/src/memfault_fault_handling_armv7_a_r.c:332